# ICALEPCS San Francisco 2013 Timing Workshop

Jukka Pietarinen

# **Topics**

- Form factors

- Firmware changes

- Event / Link rate

- Other requests

#### **Form Factors**

|                | EVG | EVR | Fan-Out |

|----------------|-----|-----|---------|

| VME            | X   | X   | X       |

| PMC            |     | X   |         |

| CompactPCI 3U  | X   | X   |         |

| CompactPCI 6U  | X   | X   | X       |

| PCI Express    |     | X   |         |

| PXI Express 3U | X   | X   |         |

| microTCA.4     |     |     |         |

### PXIe-EVG-300 Design - Features

- Basically same functionality as earlier CompactPCI modules have

- New event clock sources:

- 10 MHz PXI clock multiplied by 10

- 100 MHz PXIe clock

- In addition to

- Front panel RF input with divider

- Fractional synthesizer

#### **Future Form Factors?**

- microTCA.4 (SLAC, ESS among others)

- in development, prototype by end of 2013

- LANSCE has selected to use VPX as platform

- any other users for VPX?

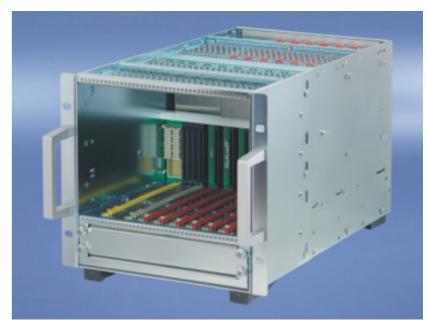

#### MTCA.4

Schroff MicroTCA.4 cube

- 180.6 mm x 148.5 mm PCB size

- High speed point-to-point links for e.g. PCI Express on backplane

- radial clocks TCLKA, TCLKB, TCLKC, TCLKD point to point connection through MCH

- eight M-LVDS bus lines e.g. for triggers, gates or slow clocks

- Rear transition module with direct connection to front board

# MTCA.4 Event Receiver (in development)

- radial clocks TCLKA, TCLKB, TCLKC, TCLKD point to point connection through MCH + redundant MCH

- eight M-LVDS bus lines

- LVDS signals to uRTM

- six front panel LEMOs (two input, four output)

- front panel micro-SCSI connector for I/O interface board with eight Universal I/O slots

- Option for routing signals through the back using an uRTM with micro-SCSI connector

- Based on Xilinx Kintex FPGA

## What is VPX (VITA 46)?

- VITA standard

- 3U / 6U form factor

- new connector for switched fabrics (PCI Express etc.)

- rugged designed with (moving) defense applications in mind

- Supports PMC and XMC

- Standard allows for lots of different (incompatible) configurations

- Rear I/O

- No timing on backplane

#### **Future Form Factors?**

- Form factors needing upgrade

- VME

- PMC -> XMC

- VPX form factor could be implemented with upgraded PMC/XMC EVR and transition module designed for VPX

# EVR Firmware changes available currently only for cPCI-EVR(TG)-300

- Motivation: ELI requirement to distribute clocks

- 0.5 Hz, 1 Hz, 10 Hz, 100 Hz, 1 kHz, 2 kHz, 100 kHz, 200 kHz

- Number of EVR prescalers 3 -> 8

- Prescalers are synchronized by "reset prescaler" event sent from EVG sequencer every 2 s

- EVR Pulse generators can be triggered from

- Distributed bus signals

- EVR Prescalers

#### **Event Link rate**

- Current limit 2.5 Gbps / 125 MHz

- Virtex II Pro (VME, PMC, cPCI 3U)

- Fan-Out limit 2.7 Gbps

- Need for new Fan-Out

- Requests: (remote) diagnostics, optical powers etc.

- Form factor? VME / cPCI / uTCA.4?

### Other Requests?

- Single Linux kernel driver to cover all event hardware

- has to cover different PCI / PCI Express chip sets

- major differences in

- interrupt handling

- firmware upgrades